CMRR(コモンモード除去比・同相信号除去比)

- Common Mode Rejection Ratio

- 共模信号消除

- 동상신호 제거

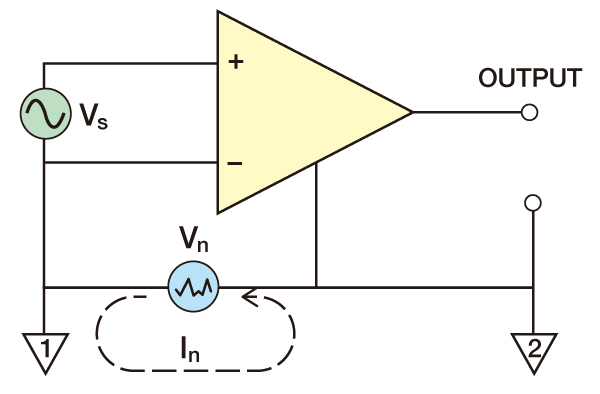

CMRR(Common Mode Rejection Ratio)とは、二つの入力回路をもつ差動増幅器などにおいて、共通する入力信号(雑音成分 Vn など)を除去できる能力のことである。

グラウンドループに商用電源信号( In )などが流れると、雑音信号( Vn )が発生し、差動増幅器に同相分として印加される。しかし、増幅器の出力に現れる同相雑音成分は極めて小さなものとなる(同相利得は小さく、理想的には零)。

差動利得(図の Vs に対する利得)をAdiffとし、同相利得(図の Vn に対する利得)をAcomとすると、CMRRは下式で定義される。

CMRR = Adiff/Acom = Adiff [dB] – Acom [dB]

例:当社製差動増幅器5307のCMRRは、商用周波数で120dB(min)

システムが大きくなると、図の 1 と 2 とは同じように見えても、電位やインピーダンスが異なるので、 1 と 2 間にグラウンドループ電流が流れて雑音となる。

Topics CMRRの実際

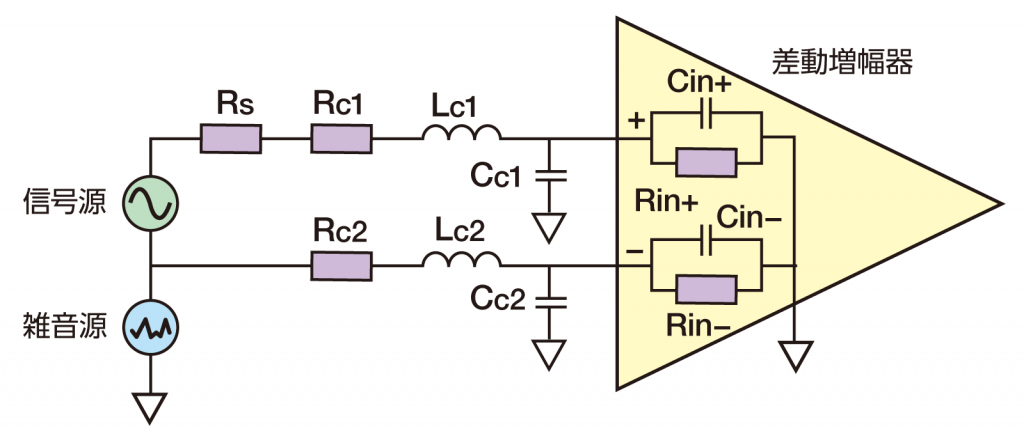

差動増幅器を実際に使用する場合には信号ケーブルが必要です。また、信号源には出力インピーダンスが存在するため、差動増幅器の使用状態における等価回路は下図のように表されます。

これらのインピーダンスがない状態における雑音源は全く同じ電圧値で差動増幅器の+と-の入力端子に加えられ、CMRRの劣化は生じません。

しかし、実際にはこれらの値が無視できず、雑音源が差動増幅器の+-に加わるときに電圧差が生じて、この差によってCMRRが劣化します。

簡単な例として、信号源インピーダンス Rs:10kΩ、差動増幅器の入力抵抗 Rin+ = Rin−:10MΩとし、

Rc など他のインピーダンスは無視すると

- 直流では、差動利得:0.9990、同相利得:0.0009990により、CMRRは20log(0.9990/0.0009990)から60.0dB。

次に Rs:10kΩ、CC1 + Cin+ = CC2 + Cin−:500pFとすると

- 10kHzでは、差動利得:0.9532、同相利得:0.2994

となり、CMRRは約10.1dBに低下します。

このように信号源から差動増幅器の+-入力端子までの電送経路にアンバランスがあるとCMRRが劣化するので注意が必要です。右図の場合には-入力に Rs と同じインピーダンスを挿入するとCMRRが改善されます。

実際の使用条件では入力部分を高域までバランスさせることは難しく、数十kHz以上で高CMRRを実現することは困難です。

- Rs:信号源出力抵抗

- Rc1 、Rc2:ケーブルの直流抵抗

- Lc1 、Lc2:信号ケーブルのインダクタンス(平行ケーブルでは1μH/m、50Ω同軸ケーブルでは250nH/m程度)

- Cc1 、Cc2:信号ケーブルのキャパシタンス(シールドケーブルでは150pF/m、50Ω同軸ケーブルでは100pF/m程度)