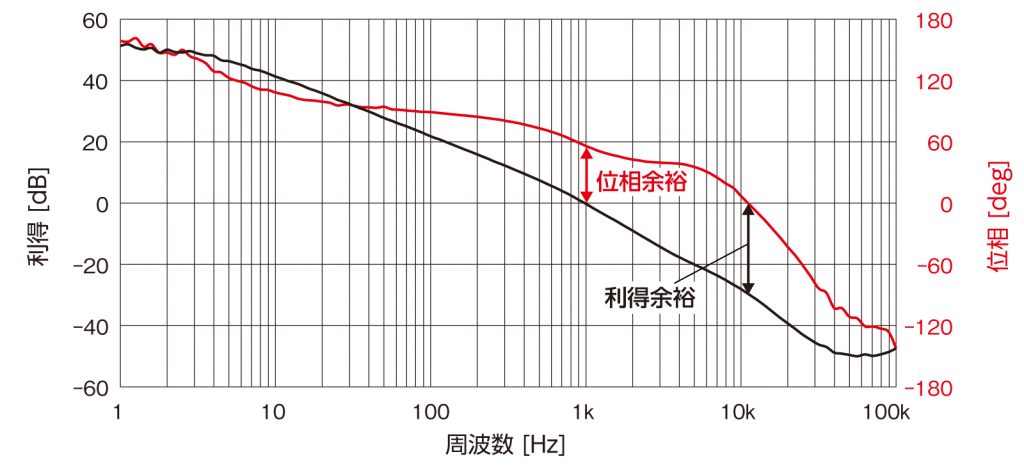

位相余裕/ゲイン余裕(利得余裕)

- Phase Margin/Gain Margin

- 相位容限/增益容限

- 위상여유/이득여유

位相余裕と利得余裕は、負帰還回路の安定性を評価する尺度である。

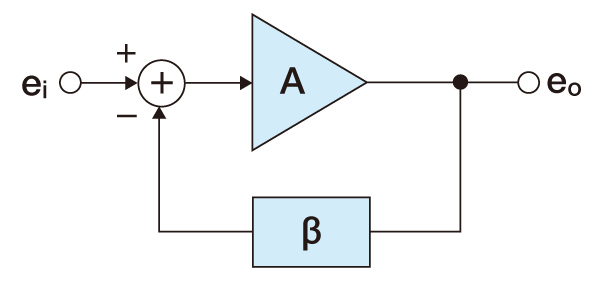

右図の負帰還回路の利得は、

となる。

アンプの入出力間の位相や利得は、相互に影響し周波数とともに変化する。入出力間の位相量が180度以上になる周波数で、利得が1(=0dB)以上あると負帰還が正帰還となってアンプは異常発振を起こす可能性がある。

以下、位相余裕と利得余裕についてFRA(周波数特性分析器)の実測データを元に説明する。

FRAでは、図1のβ回路の加算記号を+としたループ利得Aβが得られる。

位相余裕とは、図2に示すとおり、利得が0dBの周波数において位相差が0度(位相量で180度)よりどれだけ上にあるか、つまり位相差の値そのものである。

一方、位相差が0度の周波数における利得が0dBよりどれだけ下にあるかが利得余裕と定義される。

一般的に、多くの用途で適切な値としては、位相余裕が60度以上、利得余裕が10dB以上必要である。

実際の測定では、位相余裕は比較的明確に得られるが、利得余裕はノイズ等の影響で不鮮明な場合が多い。比較的高周波になると、そのときの利得がマイナスになっている場合が多い等が理由である。利得余裕が不鮮明な場合でも、位相余裕だけからでも安定性の評価は可能である。

なお、安定性の評価には、今回説明した方法(位相余裕、利得余裕)のほかにもナイキスト線図や現代制御理論等、様々な方法がある。